Nyheter

DAC utforsker rollen som AI og ML over markedene

Moscone Center, San Francisco, vil være vert for DAC 25-28 juni

OneSpin Solutions og Austemper Design Systems vil både markere verktøy for funksjonell sikkerhet verifisering. Austemper vil fokusere på oppgavekritisk systemutvikling, med KaleidoScope-verktøysuiten som støtter analog design for samtidig, feilmeldingsformidling med blandet signal. Den automatiserte verktøypakken har sikkerhetsanalyse, syntese og verifikasjonsfunksjoner for sertifiseringsorienterte applikasjoner. Den brukes til storskala automotive design i ADAS og autonom kjøring. Den samtidige feil simuleringen inkluderer simuleringer anbefalt av ISO 26262 for å overholde ASIL krav.

Selskapet har nylig samarbeidet med OneSpin Solutions for å vedta en verktøystøttet metodikk for funksjonelle sikkerhetsapplikasjoner, som kombinerer en design- og verifikasjonsflyt som vil bli demonstrert på OneSpin-kabinen. Maskinvare sikkerhetsmekanismer settes inn i chip design og OneSpin Solutions 'verktøy formelt verifiserer maskinvaresikkerhetslogikken. Likestillingskontroll sikrer at den innsatte sikkerhetslogikken ikke påvirker den vanlige funksjonaliteten, og feilsøkingsanalysen verifiserer at sikkerhetsmekanismer fungerer riktig i tilfelle tilfeldige feil.

OneSpin fremmer også sitt Tool Qualification kit, etter verifisering av TÜV SÜD av verktøyutviklingsprosessene. Det første settet er tilgjengelig for selskapets 360 EC-FPGA EDA-verktøy, en automatisk sekvensiell ekvivalenskontroll som forhindrer FPGA-designstrømmer fra å innføre implementasjonsfeil. Kittet er sertifisert til ISO 26262, IEC 61508 og EN 50128.

FPGA innsikt

Fortsatt med FPGA-design, Plunify har samarbeidet med Xilinx for å tilby Vivado designpakken i skyen, via Plunify Cloud-plattformen. Designere betaler så lite som 50c for å samle et Vivado-prosjekt på Amazon Web Services (AWS) -skyen, inkludert lisenser.

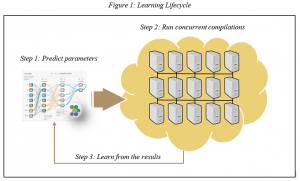

Selskapet vil også demonstrere forbedringer av InTime timing-lukkingsprogramvaren for å optimalisere FPGA-timing i skyen (Figur 1). InTime Optimization Metodology kan forbedre klokkefrekvensen med 20 til 80% og møte timing krav i dager, i stedet for uker via maskinlæring. Programvaren akselererer også tidsavslutning og optimalisering og er tilgjengelig via skyen.

Selskapet vil også demonstrere forbedringer av InTime timing-lukkingsprogramvaren for å optimalisere FPGA-timing i skyen (Figur 1). InTime Optimization Metodology kan forbedre klokkefrekvensen med 20 til 80% og møte timing krav i dager, i stedet for uker via maskinlæring. Programvaren akselererer også tidsavslutning og optimalisering og er tilgjengelig via skyen.

Fremme eFPGA-teknologi, Achronix Semiconductor samarbeider med IP-spesialist CAST for å øke gjennomstrømmingen og gjøre besparelser i minneoppbevaring.

De to utstillerne vil forklare hvordan CASTs lossless komprimerings-IP har blitt portet til Achronix FPGA-porteføljen for bruk i datasenter og mobilkants dataoverføringsprogrammer. Maskinvareimplementeringen av den lossless komprimeringsstandarden for Deflate, GZIP og ZLIB, er kompatibel med programvareimplementeringer som brukes til komprimering eller dekomprimering for å gi opptil 100 Gbit / s gjennomstrømning med lav komprimering og lav ventetid, kombinert med Speedcore eFPGA-teknologi for å flytte og lagre store data ved lavt strømforbruk.

CAST har levert sin IP til Achronix FPGAs

Energieffektivitet

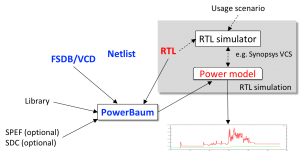

Snakker om strømstyring, en annen utstiller, Baum, identifiserer energieffektivitet som det mest underutviklede området i chipdesign. Den automatiske effektanalysen og modelleringsverktøyet er designet for automotive, IoT, mobil, nettverk og serverprosjekter. PowerBaum 2.0 (Figur 3) støtter dynamisk og statisk kraft, tar inn RTL- og netlist-beskrivelser, og legger til støtte for strømanalyse med maskinvareemulering. Dette, sier selskapet, tillater ingeniører å fikse strømbrudd i realistiske programvare scenarier. Verktøyet støtter også analyse med vilkårlig temperatur som spesifiseres av designere, for å vurdere effekten av temperatur på et designs strømforbruk.

På DAC, vil selskapet også introdusere PowerWurzel, en gate nivå strømanalysemotor som skal integreres med PowerBaum for kraftmodellering.

Figur 3 Baums verktøy analyserer energieffektivitet

Cloud-basert SoC design og verifikasjon verktøy for IC design fra metrics inkludere Cloud Simulator og Verification Manager, designet for å håndtere simuleringskrav og ressurser, justere dem opp eller ned hvert minutt. Selskapet hevder at Google Cloud muliggjør ubegrenset UVM-kompatibel SystemVerilog-simuleringskapasitet og innfødt, webbasert verifiseringsbehandling for raskere regresjonstider, reduserte kodeløpsfeil og forutsigbar kodedekning.

Bortsett fra utstillere, arrangerer arrangementet tekniske økter og et program av keynotes som adresserer aktuelle områder. I år, for eksempel, vil Cadence være vert for 'Funksjonell sikkerhet og pålitelighet for automotive applikasjoner', og en på maskinlæring ('Maskinlæring tar talegjenkjenningsprestasjon til neste nivå'). En keynote av Anna-Katrina Shedletsky, Instrumental, mandag 25. juni, vil fokusere på "Automating Intelligence: Machine Learning and the Future Of Manufacturing". Bruke ML og AI for sosialhjelpsrobotikk (SAR) utforskes i torsdagens hovedbilde av Maja Matarić, Universitetet i Sør-California, som vil presentere "Automation vs Augmentation: Sosialt Hjelpende Robotocs og Fremtidens Arbeid".

En annen keynote fortaler RISC-V som et middel for å frigjøre arkitekter fra proprietære instruksjonssettede arkitekturer (ISAer). David A Patterson, Google og University of California, vil presentere "En ny gylden tidsalder for dataarkitektur: Domain Specific Accelerators og Open RISC-V".

Et nytt område i år på DAC er Design Infrastructure Alley. Initiativet fra ESD Alliance og forening for profesjonelle profesjonelle profesjonelle er et område dedikert til IT-infrastrukturen for utforming av elektroniske systemer og komponenter. I tillegg til databehandling og lagringskrav for utforming og styring av bruk av skyen, er det et dedikert Design-on-the-Cloud paviljongteater som diskuterer lisenshåndtering, nettberegning og datasikkerhet.